# VLSI Design of Carry Select Adder Based Vedic Multiplier With High Speed and Low Area

P.Kusuma Vani,

Assistant professor, Raghu institute of technology, Vishakhapatnam G.Umadevi, Assistant professor, Nalla Narasimha Reddy group of Institutions, Hyderabad

**Abstract:** In this paper, Vedic multiplier is planned utilizing zone proficient Carry Select Adder (CSLA). As the duplication is the procedure of resulting expansion, snake is vital square in usage of multiplier. Computerized snake has issue of convey proliferation, consequently convey select snake is utilized rather than basic Ripple Carry Adder (RCA). Convey select snake is known to be one of the quickest viper structures. Here Vedic multiplier is actualized rather than ordinary multipliers like include and move multiplier, cluster multiplier and so on. The objective of this paper is to plan Vedic multiplier dependent on across and vertical calculations utilizing region effective CSLA. Traditional CSLA plans like Binary to Excess one Converter (BEC) based CSLA and Modified CSLA (MCSLA) are contrasted with proposed CSLA plan with demonstrate its effectiveness. It indicates improved execution as far as zone. This remodeled CSLA and 16% less region than Vedic multiplier utilizing BEC-based CSLA. Proposed configuration is additionally contrasted and the Booth multiplier. Proposed multiplier demonstrated more magnificent outcomes than Booth multiplier.

Keywords: Binary to Excess one Converter (BEC), Carry Select Adder (CSLA).

### 1. INTRODUCTION

There is blasting being used of convenient gadgets in everyday life at last interest for superior Very Large Scale Integration (VLSI) frameworks have been expanded. To adapt to these requests different specialists are creating improved VLSI frameworks as far as region, control, delay and so on. Multiplier is one of the essential squares in number juggling unit. Rapid and region proficient multiplier is required in different Digital Signal Processing (DSP) calculations. Vedic duplication is utilized in different DSP applications like convolution, Fast Fourier Transform and chip applications. Vedic arithmetic is an old numerical system. Vedic is a word gotten from "Veda" and its importance is

"storage facility of all learning" [1]. These scientific procedures require less territory and they work with fast. 16 sutras are premise of Vedic science. In this paper, 8 by 8 multiplier is actualized utilizing "Urdhva-Tiryakbhyam - Vertically and transversely." Whatever remains of the paper is as per the Urdhva-Tiryakbhyam following. Prologue to technique is given in segment II. Engineering of Vedic multiplier is clarified in area III. Regular convey select snake and proposed structure are exhibited in segment IV and V separately. Execution results and end are given in segments VI and VII separately.

# 2. ANCIENT VEDIC MATHEMATICAL ALGORITHM:

By applying sutras Vedic arithmetic purposes complexicty of computations. It requires less computation time and less equipment for implementation. These sutras are essentially utilized for decimal augmentation here it is incarporated to twofold duplication.

A.Urdhva–Tiryakbhyam Sutra(Vertically and Crosswise)

In this paper execution of Vedic increase system to be specific "Urdhva-Tiryakbhyam – Vertically and transversely" is illustrated. This procedure is increasingly well known for its rapid filling in as it creates incomplete items in parallel way and after that including fractional items at the same time. There is fortifying need of rapid information handling frameworks. Vedic multiplier assuages this need without expanding power utilization. It has less intricacy contrasted with stall multiplier. Vedic multiplier requires less equipment. Therefore Vedic multiplier gives various points of interest as far as territory, power, deferral and intricacy.

B. Example for Vedic increase (Decimal Multiplication)

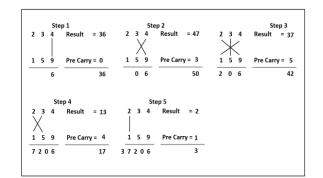

Two decimal numbers 234 and 159 are considered. Increase of these two numbers (234 X 159) is depicted with the line outline for clear understanding as appeared in fig.

1. At initial, two numbers appeared with line are duplicated, 2 digits yield is produced. One's place of this created outcome is put away as one's place of conclusive item and ten's place of the produced yield is snared as pre-convey for the subsequent stage. Along these lines the procedure propagated. So, all in all, there is more than one digit to duplicate then increase those digits appeared with lines and aggregate each one of those created items. Yield of this summation is again put away in conclusive outcome with sending pre-convey to following stages as clarified before. Along these lines procedure keeps on getting last consequence of duplication of two numbers (234 X 159).

Fig. 1. Multiplication of two decimal numbers

#### 3. ARCHITECTURE AND IMPLEMENTATION OF VEDIC MULTIPLIER

In the previous section sacred writing multiplication technique for decimal numbers is delineate. This section explains design of N by N bit multiplier factor. The sacred writing multiplication technique is used for multiplication of binary numbers. Implementation a pair of|of two} X 2 sacred writing multiplier factor block is prime necessary within the implementation of four X four eight|and eight} X 8 sacred writing multiplier factor design. during this section implementation a pair of|of two} X 2, four X four eight|and eight} X 8 sacred writing multiplier factor design ar explained.

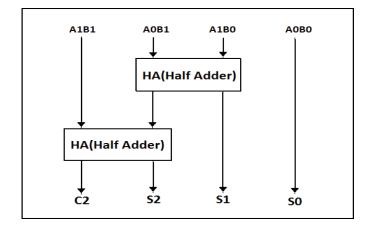

A. two X two sacred writing multiplier factor Block Here, actual Urdhva -Tiryagbhyam Sanskrit literature multiplication technique is applied by to two binary numbers with two bits every. Considering 2 numbers ar A and B wherever A = A1A0 and B = B1B0. Least important Bit (LSB) of 1st variety A that's A0 and LSB of second variety B that B0 ar increased with one another (vertical). Generated product is saved as LSB of ultimate result. Thus, AND circuit is employed for multiplication of A0 and B0. Fig. 2, shows two X two multiplication method. Next step is to multiply LSB of variety A with MSB of variety B that's (A0 X B1) and MSB of variety A with LSB of variety B that's (A1 X B0). Thus, 2 AND gates ar needed for this multiplication.

Fig. 2. 2 X 2 Vedic multiplier architecture

These generated product area unit intercalary that's (A0 X B1) + (A1 X B0) exploitation 0.5 adder. This summation generates output of two bits. LSB of this generated output is loaded as second little bit of upshot and mutual savings bank of this generated output is loaded as pre carry for next step. Last step is multiplication of mutual savings bank of A with mutual savings bank of B that's (A1 X B1). One AND circuit is employed for this multiplication. This generated product is intercalary with pre carry of previous step. so once more an extra 0.5 adder is needed for it. This 0.5 adder generates two bits output that is taken as third and fourth little bit of upshot. the ultimate result's given by C2S2S1S0. during this means two X two sacred writing multiplication method is applied. {the two|the two} X 2 sacred writing multiplication method is shown with equations.

$$\begin{array}{l} S_{0}=A_{0}B_{0} \qquad (1) \\ C_{1}S_{1}=A_{0}B_{1}+A_{1}B_{0} \\ C_{2}S_{2}=C_{1}+A_{1}B_{1}\left(3\right) \end{array} \tag{2}$$

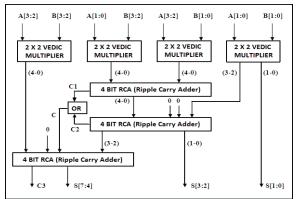

# B. 4 X 4 Vedic Multiplier Block

In this segment 4 X 4 Vedic multiplier design is talked about. Consider two 4-bits numbers, for example, An and B where A = A3A2A1A0 and B = B3B2B1B0. The LSBs of two numbers (A0 X B0) are duplicated to produce LSB S0 of conclusive outcome. Same methodology is chased here as 2 X 2 Vedic duplication system examined before. At first pre-convey is set to zero. In every single step created convey is sent to following stage and procedure goes

on. Toward the end C6 and S6 is gotten. Yield lines C6S6S5S4S3S2S1S0 gives at long last created outcome.

The 4 X 4 Vedic duplication square chart is appeared in fig. 3. Here, 2 X 2 Vedic multipliers are utilized to execute 4 X 4 Vedic multiplier to create incomplete item. Three swell convey adders of 4 bits each are utilized for expansion of created fractional items. The convey yield of initial two swell convey adders are ORed and yield of this OR entryway is given to next swell convey viper. Zero sources of info are given to a portion of the swell convey adders wherever required. The course of action of swell convey adders is made in such way that calculation time required for entire duplication process is decreased and speed of working is expanded.

Fig. 3. 4 X 4 Vedic multiplier architecture

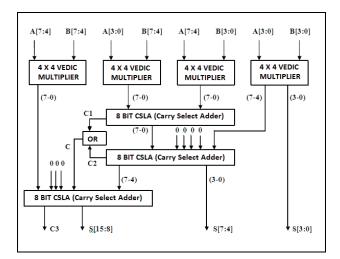

C.eight X 8Vedic multiplier factor Block Here, implementation of eight by eight Vedic multiplier factor is made public. think about 2 8-bits binary numbers specifically A and B wherever A =A7A6A5A4A3A2A1A0 and B =B7B6B5B4B3B2B1B0.

8 X eight Vedic multiplication method is mirror to four X four Vedic multiplier factor expressed within the previous sub-section B. Pre-carry initially step is about to zero. In each step generated carry is shifted to next step for addition and method continues. At the top C14 and S14 is obtained. Finally generated result's given terms in of C14S14S13S12S11S10S9S8S7S6S5S4S3S2S1S0. Implementation of eight by eight Vedic multiplier factor is clearly understood from the diagram as shown in fig. 4. Here, four four X four Vedic multiplier factor blocks and 3 carry choose adders of eight bits every square measure used. The arrangement of the carry choose adders is created in several means specified it needs less computation time. a number of the carry choose adders square measure given with zero inputs, where needed.

Output of middle multipliers square measure

superimposed exploitation initial CSLA. Output of initial CSLA and initial Vedic multiplier factor square measure superimposed exploitation second CSLA. Carry outputs from initial 2 CSLAs square measure ORed and given as input to the third CSLA to get upshot.

Fig. 4. 8 X 8 Vedic multiplier architecture

# 4. CONVENTIONAL CARRY SELECT ADDER

In [1] Vedic number is enforced mistreatment BEC based mostly carry choose adder whereas in [8] Vedic number is enforced with MCSLA. Still there's scope to use additional economical carry choose adder rather than CSLA [2] [3]. Therefore new Vedic number is projected mistreatment additional economical carry choose adder. during this paper, eight X eight Vedic number is enforced as shown in fig. 4.

# A. MCSLA

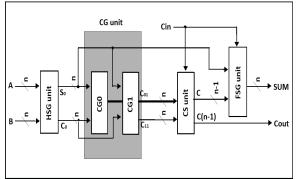

B. K. Mohanty and S. K. Patel proposed adjusted CSLA [3]. The square graph of that convey select viper is appeared in fig. 6. This CSLA has one Half Sum Generation (HSG) unit, one Final Sum Generation (FSG) unit, one Carry Generation (CG) unit, and one Carry Selection (CS) unit. The CG unit made out of two CGs (CG0 and CG1) comparing to include convey '0' and '1' [3]. Two n bit operands (An and B) are given to HSG unit that creates n bits S0 and n bits C0. These created S0 and C0 are given to CG0 just as CG1 and n-bit full convey words C01 and C11. CS unit chooses one of the yields from full convey words C01 and C11. In the event that Cin ='0' at that point CS will choose C01, else it will choose C11. By utilizing this adjusted CSLA, Vedic multiplier [8] is actualized.

Fig. 5. Modified CSLA

#### 5. PROPOSED DESIGN

BEC-based CSLA and MCSLA are quickly examined and seen the likelihood of planning increasingly improved CSLA. Proposed CSLA comprises of essentially two units 1) whole and convey age unit 2) total and convey choice unit. Repetitive activities present in past CSLA plans are distinguished and disposed of. This has assisted lessen number of doors required for the proposed structure. So the point is to lessen number entryways required for the plan of CSLA. Limiting the quantity of doors of configuration includes two stages

• Generate all the prime implicants for the given rationale work f [9].

• Find the arrangement of basic prime implicants.

As needs be new territory effective convey select viper is planned.

#### A. Single Stage CSLA

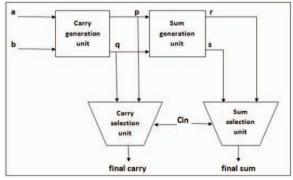

In proposed structure some rationale details are made. Contingent on the whole and convey capacities equivalent to '1' prime implicants are noted down. Basic prime impicants are joined so last aggregate and last convey can be produced. Separate aggregate and convey choice units are utilized after entirety and convey age units to dispose of the repetitive activities. At first, single stage CSLA is executed. Contingent on bit example of info convey 'Cin' last aggregate and convey is chosen. 'On the off chance that Cin = 0' at that point convey determination unit will choose yield 'p' from convey age unit else it will choose 'q'. On the off chance that Cin = '0' at that point total choice unit will choose yield 'r' from aggregate age unit else it will select's' as appeared in the fig. 6

Fig.6. Single stage CSLA

### B. Multistage CSLA

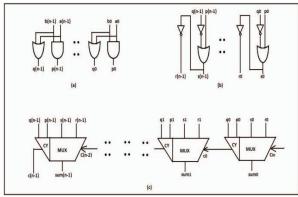

By falling single stage CSLAs, multistage CSLAs are shaped. Here various piece widths of CSLA are planned, for example, 8-16-32 bits. Proposed CSLA structure at door level is appeared in fig. 8 where fig. 8 (a) represents entryway level structure of convey age unit. Entryway level execution of total age unit is appeared in fig. 8 (b). Door level structure of total and convey choice unit is appeared in fig. 8 (c). For determination of aggregate and convey multiplexer is used. These are 4:2 multiplexers acquired from two 2:1 multiplexers one for convey choice and other for entirety determination.

Multistage CSLA of 'n' bit width is appeared in fig. 9. Conditions for aggregate age convey age just as whole and convey determination are given underneath.

Fig. 7. (a) Carry generation unit (b) Sum generation unit (c) Sum and carry selection unit

## 6. RESULTS AND DISCUSSIONS

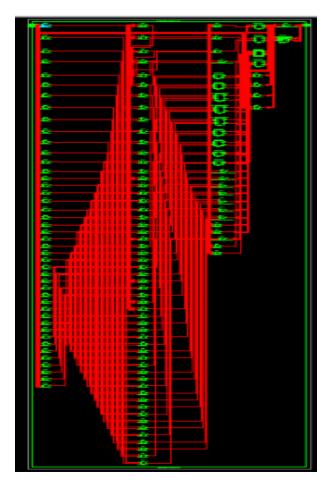

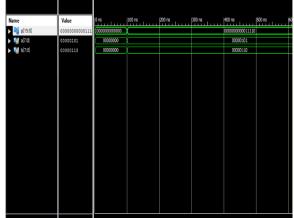

In the Xilinx ISE we have generated RTL Schematic and simulation output for the Vedic multiplier have been shown below.

Fig8: RTL Schematic for the proposed design

Fig9: Simulation output for the proposed design

# 7. CONCLUSIONS

Vedic number victimization carry choose adder is enforced here. initially typical CSLAs like (BEC based mostly CSLA and MCSLA) yet as planned CSLA square measure enforced. in keeping with the results obtained, it's all over that planned

carry choose adder needs less range of gates than each MCSLA and BEC based mostly CSLA. On a mean, planned carry choose adder needs twenty one roughly space than MCSLA and four hundred and forty vards less space than BEC based mostly CSLA for various bit widths. therefore planned religious text number is enforced victimization this improved CSLA. planned religious text number needs less range of gates. On a mean, planned religious text number needs 6 June 1944 less space than religious text number victimization MCSLA and 16 PF less space than religious text number victimization BEC based mostly CSLA. therefore planned religious text number is a lot of area-efficient than typical religious text multipliers. planned religious text number is additionally compared with typical religious text multipliers in terms of delay. planned religious text number needs less delay than religious text number victimization MCSLA whereas it needs a lot of delay than religious text number victimization BEC - based mostly CSLA. planned religious text number is additionally compared with the Booth number. planned religious text number has or so forty three roughly space than Booth number. planned number is quicker than Booth number because it has or so Vday less delay than Booth number. Thus, planned religious text number is superior to Booth number in terms of delay yet as space.

### REFERENCES

- P. Y. Bhavani, G. Chokkakula, S. P. Reddy and N. R. Samhitha, "Design of low power and high speed modified carry select adder for 16 bit Vedic multiplier,"IEEE, Feb 2014.

- [2] B. Ramkumar and H. M. Kittur, "Low-power and area-efficient carry- select adder," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 20, no. 2, pp. 371–375, Feb. 2012.

- [3] B. K. Mohanty and S. K. Patel, "Area-delaypower efficient carry- select adder," IEEE Trans. Circuits and Systems. vol. 61, no. 6, pp. 418-422, June 2014.

- [4] R. P. Rajput and M. N. Shanmukha Swamy, "High speed modified Booth encoder multiplier for signed and unsigned numbers", UKSim 14<sup>th</sup> International Conference on Modelling and Simulation, pp. 649- 654, March 2012.

- [5] H. Thapliyal and H. R. Arbania. "A timearea-power efficient multiplier and square architecture based on ancient Indian Vedic mathematics", proceedings of the 2004, International Conference on VLSI (VLSI'04), Las Vegas, Nevada, pp. 434-439, June 2004.

- [6] H. D. Tiwari, G. Gankhuyag, C. M. Kim, and Y. B. Cho, "Multiplier design based on

ancient Indian Vedic mathematics", Proc. Int SoC Design Conf., pp.65-68. 2008.

[7] H. Thapliyal and M. B. Srinivas, "VLSI implementation of RSA encryption system using ancient Indian Vedic mathematics", Center for VLSI and Embedded System Technologies, International Institute of Information Technology Hyderabad-500019, India.