# A Review on: Priority Based Arbiter for NoC Router

Neha B.Kowale1, Prof. S D.Kambale2, Prof. M N.Thakhare3

1 Mtech(IVth) Sem, SDCE Selukate, Wardha India, nehakowale@gmail.com.99751892024

2AssistantProfessor, Department of ElectronicsEngineering, SDCE, Wardha India,

sanghpal.kamble@gmail.com,9960778311

3Assistant Professor, Department of Electronics and Telecommunication, BDCE, Sevagram India

3Assistant Professor, Department of Electronics and Telecommunication, BDCE, Sevagram India <u>mnt\_ent@rediffmail.com</u>,9423620513

**Abstract:** NoC means Network on Chip is a new method for communication to solve a problem that challenges system on chip. In router, Arbiter is used in network on chip when number of input are requested for same output port, the arbiter has generate the grant signal on the basis of that number of input port getting a priority and the input port transmit a packet to output port. Dynamic priority of a packet is given according to the traffic load of previous router. In certain router, if many packets request the same output channel, the router need to choose one of these packet, and deliver it to next router. In the dynamic priority based round robin arbiter in this they can reduced power consumption and area gate count. In this paper we will design dynamic priority based matrix arbiter and also compare the parameter like area, delay, and low latency which we will improve the speed of communication on NoC router.

**Keywords-** Network on Chip (NoC) 1

#### 1. INTRODUCTION

In recent years, many researches of the NoC design make on effort to improve the performance by using routing algorithm or chaining router architecture Network-On-Chip (NoC) consists of routers, links, and network interfaces.(1) Routers direct researches of the NoC design make on effort to improve the performance data over several links (hops).

The NoC architecture has two parts: router and data link. The router can store and forward data, and the data link can transmit signals from one router to its neighbor. The input buffer stores the input data temporarily, The arbiter receives requests from input buffers and allocates virtual channels to requests and then gives grant signals to request initiators. The crossbar switches granted input requests and forwards the request data to data link

and then the request data is transmitted to the next hop router through data link. In the NoC it consist of an NoC architecture and NoC router architecture which design a router it consist of three parts arbiter, buffer, crossbar In the Dynamic Priority the different channels are requested for different locations then the dynamic priority arranged that dynamic priority arranged in then equilibrium. Dynamic priority of a packet is given according to the traffic load of previous router. In certain router, if many packets request the same output channel, the router need to choose one of these packet, and deliver it to next router. Dynamic priority based Round Robin Arbiter will operates on the principle that a request that was just served

should have the highest priority and next round of arbitration. In this paper we will design dynamic priority based matrix arbiter which will reduced time and improve the speed to make better transmission of signal.

## 2. LITERATURE REVIEW

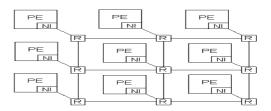

# NoC ARCHITECTURE

In the NoC architecture the Network-On-Chip (NoC) consists of routers, links, and network interfaces. Routers direct data over several links (hops). Topology defines their logical lay-out (connections).Network-on-Chip (NoC) is an alternative for communication in SoCs with ability of providing high throughput, low latency and scalability..NoC architectures are based on packet-switched networks and circuit-switched networks. A typical NoC consists of computational processing elements (PEs), network interfaces (NIs), and routers.. The NoC architecture has two parts router and data link. (2)The router can store and forward data and the data link can transmit signals from one router to its neighbor.

International Journal of Research in Advent Technology (E-ISSN: 2321-9637) Special Issue 1st International Conference on Advent Trends in Engineering, Science and Technology "ICATEST 2015", 08 March 2015

## Fig.1

This paper proposes the power efficiency of NoC (network on chip) is becoming a new research direction. They had proposed an innovative powerefficient architecture of input buffer of NoC, which makes use of the mentioned characteristics, can improve the power efficiency of the NoC of tiled CMP significantly. As an important part of a tiled CMP, the NoC architecture is composed with two parts: router and data link. The router is a module which can store and forward data, and the data link can transmit signals from one router to its neighbour. Since the energy consumption of an operation depends on the data of current cycle as well as its continuously previous cycle, They used the data transition as the independent variable for precision. The digital signals transmitted on NoC are occurred by cache coherence protocol .[1]

## NoC ROUTER ARCHITECTURE

The NoC router architecture consist of three bolck Arbiter, buffer, crossbar. The input buffer stores the input data temporarily, The arbiter receives requests from input buffers and allocates virtual channels to requests and then gives grant signals to request initiators.(6) The crossbar switches granted input requests and forwards the request data to data link, and then the request data is transmitted to the next hop router through data link.

In this paper, A NoC Router if more than one input is request for the same output the arbiter is used. Here we are explaining the behavior of Round Robin Arbiter in NoC Architecture. The Round Robin Arbiter operates on the principle that a request which was just served should have a lowest priority on the next round of arbitration. It keeps the updated status of all the ports and knows which ports are free and which ports are communicating with each other. Packets with the same priority and destined for the same output port are scheduled with a Round-Robin Arbiter. In the Round Robin Arbitration scheme, which may be granted that all input request are treated fairly. Hence they had proposed arbiter is suitable for NoC design.[2]

# ARBITRATION TECHNIQUES

A NOC, which is capable of supporting different classes of service levels such as best effort and guaranteed traffic, needs to support an arbitration mechanism. This arbitration mechanism schedules a flit for transmission on the output path. There are various arbitration mechanisms such as RR (Round Robin), Matrix Arbiter.

#### DYNAMIC PRIORITY

In the Dynamic Priority the different channels are requested for different locations then the dynamic priority arranged that signal then dynamic priority arranged in equilibrium. Dynamic priority of a packet is given according to the traffic load of previous router.(3)In certain router, if many packets request the same output channel, the router need to choose one of these packet, and deliver it to next router.

1. Dynamic priority based Round Robin Arbiter: It operates on the principle that a request that was just served should have the highest priority and next round of arbitration.

In this paper they have focused that Dynamic priority of a packet is given according to the traffic load of previous router. In certain router, if many packets request the same output channel, the router need to choose one of these packet, and deliver it to next router. For a new packet control circuit is implemented to decide whether the congestion happen and whether the priority scheduler should be used or not. The transmission latency can be reduced with few area overhead. As the NoC demand increased, This method provides a very good solution for heavy traffic loading They proposed method can reduce the transmission latency in uniformly distributed traffic and in hotspot traffic when compare with the conventional router. Five different traffic types are used to measure the method's performance. The first one is uniform traffic and the second one is hot-spot traffic. The packet routing path of these two types are not fixed. The third one is first-transpose traffic and the fourth one is bit-reversal traffic. Dynamic priority of a packet is given according to the traffic load of previous router. Network-on-Chip (NoC) architecture has been design to solve the complex on-chip communication problem in future SoC systems by using modular and scalable structure. [3]

# **ROUND ROBIN ARBITER**

In Round Robin Arbitration scheme when all input port are requesting for same output port the Round Robin Arbiter checks the destinations address of each port. If the destination address is same then Round Robin Arbiter use arbitration algorithm. In this algorithm.(2) Round Robin Arbiter gives the Priority to input request. Accordingly grant signal is generated and source packet is transmitted to destination through crossbar.

International Journal of Research in Advent Technology (E-ISSN: 2321-9637) Special Issue

1st International Conference on Advent Trends in Engineering, Science and Technology

"ICATEST 2015", 08 March 2015

In this paper, A NoC Router if more than one input is request for the same output the arbiter is used. Here we are explaining the behavior of Round Robin Arbiter in NoC Architecture. The Round Robin Arbiter operates on the principle that a request which was just served should have a lowest priority on the next round of arbitration. It keeps the updated status of all the ports and knows which ports are free and which ports are communicating with each other. Packets with the same priority and destined for the same output port are scheduled with a Round-Robin Arbiter. In the Round Robin Arbitration scheme, which may be granted that all input request are treated fairly. Hence they had proposed arbiter is suitable for NoC design.[4]

In this paper, they have shown the Hierarchical Round Robin Arbiter (HRRA) a high-speed and area-efficient RRA for NoC applications, which completes the arbitration in one short clock cycle. HRRA is unique in the way it divides the arbitration process into simpler consecutive steps, where at each step a novel high-performance and light-weight RRA is used, They show that HRRA outperforms the previous work for all three performance parameters (clock frequency, area and power) as the design scales to large number of inputs. They performance of the HRRA to the performance of PPE, they have implemented different size (8, 16, 32,and 64 input) HRRAs and PPEs.[5]

# **MATRIX ARBITER**

In Matrix arbitration scheme when all input port are requesting for same output port then Matrix arbiter first trap source and destination address from buffer and forms the Matrix . The Matrix arbiter uses same algorithm as that of Round Robin Arbitration Algorithm.(6) In case Matrix Arbiter Priorities of input packet to transfer the packet from source to destination are arranged in rotation among source address in the Matrix form. Hence Matrix arbiter is basically based on rotation priority to avoid the drawback of fixed priority based Round Robin Arbiter.

In this paper,they have focused Design Matrix Arbiter for NoC architecture. In the matrix arbitration when all input packet have the same priority request for same output port then matrix arbiter generate the matrix depending upon input and this case the destination address is not same so every input port getting a priority so they have to transfer data from source to destination. When all input port are request for same output port in this situation matrix arbiter first form a matrix 5\*5. After that matrix arbiter assign the Priority to all input request and generate the grant signal. In this

paper they are analyze the Area, power. In the matrix arbiter the input request is granted according to priority matrix. the round robin arbiter use less resources as compared to matrix arbiter & the matrix arbiter consume more resources because of that it uses maximum clock frequency. The matrix arbiter has higher throughput and more computational speed. As the number of input increase power consumption increases. [6]

## 3. PROPOSED METHODOLOGY

In the proposed work, we are going to design the dynamic priority for matrix arbiter in NoC router to reduce the delay. In this methodology we will reduced Area & power. In proposed these two arbiter improve the speed of packet transmission from source to destination and it is beneficial for NoC Router. Comparison and study of dynamic arbiter based various traffic channel

## 4. CONCLUSION

In this paper we will design dynamic priority based arbiter for NoC router, the NoC router gives low latency & Reduction in delay along with the area gate count. With the different arbitration techniques.

## REFERENCES

- [1] "An Innovative Power-Efficient Architecture for Input Buffer of Network on Chip"

- Proceedings of the 2007 IEEE International Conference March Shenzhen, China Kun Huan Jun Wang Ge Zhang Key Laboratory of Computer System and Architecture, Institute of Computing Technology, Chinese Academy of Sciences, Beijing.

- [2] "The Behavior of Round Robin Arbiter in NOC Architecture" International Journal of Engineering and Innovative Technology (IJEIT) .Suyog K. Dahule, Reetesh V. Golhar, Mangesh D. Ramteke. November 2013

- [3]"A Priority based Output Arbiter for NoC Router" IEEE Transaction Cheng-Hao Chan, Kun-Lin Tsai, Feipei Lai, and Shun-Hung Tsai 2011.

- [4] "Design & Simulation of Round Robin Arbiter for NoC Architecture" International Journal of Advanced Research in Computer Science and Electronics Engineering(IJEAT) Mr.Suyog K.Dahule, Dr.M.A.Gaikwad. July 2012

- [5] "Hierarchical Round Robin Arbiter for High-Speed, Low-Power, and Scalable Networks-on –Chip" Journal N. Sertac Artan, Ming Yang, and H. Jonathan Chao

- [6] "Design & Analysis of Matrix Arbiter for NoC Architecture" International Journal of Advanced Research in Computer Science and

International Journal of Research in Advent Technology (E-ISSN: 2321-9637) Special Issue 1st International Conference on Advent Trends in Engineering, Science and Technology "ICATEST 2015", 08 March 2015

- Electronics Engineering(IJEAT) Mr.Suyog K.Dahule, Dr.M.A.Gaikwad. July 2012

- [7] "Dynamic Router Design For Reliable Communication in Noc" International Journal of Innovative Research in Computer and Communication Engineering (ICGICT'14)Mr. G.Kumaran1, Ms. S.Gokila. March 2014

- [8] "An Energy and Performance Exploration of Network-on-Chip Architectures" IEEE transactions on very large scale integration (VLSI) systems, by Arnab Banerjee, Pascal T. Wolkotte, Robert D. Mullins, Simon W. Moore, and Gerard J. M. Smit.March 2009

- [9] "Design and Analysis of On-Chip Router for Network On Chip" International Journal of Computer Trends and Technology. Ms. A.S. Kale, Prof. M.A.Gaikwad August 2011.

- [10] "Survey Exploration of Network-on-Chip Architecture" "International Journal of Computer Trends and Technology N.Ashokkumar1 P. Nagarajan2 S.Ravanaraja3.